February 2

La maggior parte Universal Asynchronous Receiver Transmitter (UART) che ho trovato on-line, sono troppo complicato e difficile da capire, qui mi spiegherà qualche semplice teoria e anche il codice su come costruire uno.

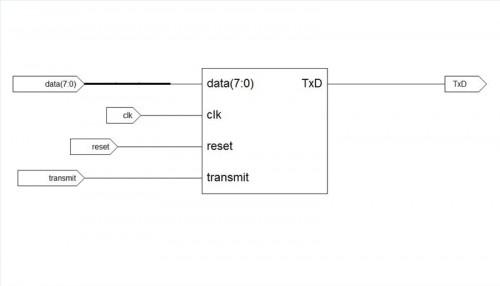

1 In primo luogo permette di parlare di come trasmettitori funzionano. Il principio di base è di inviare più bit di dati su una singola linea. Nel nostro trasmettitore, questi dati è parallelo, tuttavia per ridurre il numero di fili necessari, usiamo comunicazione seriale che viene convertito in parallelo alla ricezione.

Le cose di base di cui abbiamo bisogno sono i seguenti:

Un divisore di clock (il nostro contatore)

Questo ci si permette di inviare i dati ad una certa velocità (velocità di trasmissione). Il nostro ricevitore campione e prendere il bit di dati per bit.

Un registro a scorrimento

Abbiamo bisogno di sapere quanti bit alla volta stiamo trasmettendo, il nostro registro a scorrimento avrà un bit di start, bit di dati, bit di parità (opzionale), punta fine.

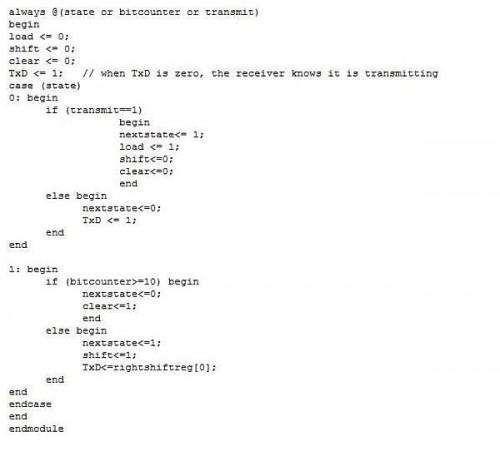

Un diagramma di stato

Prima di scrittura qualsiasi codice, dobbiamo pensare a quello che ci serve per creare e il modo migliore è la creazione di un diagramma di stato del nostro design. Sappiamo che per un trasmettitore abbiamo bisogno di 2 stati, IDLE e trasmettere.

Dopo aver avuto un diagramma di stato, ora siamo in grado di calcolare ciò che il nostro contatore sarà. Questo viene fatto utilizzando:

contatore = velocità di clock FPGA / velocità di trasmissione

In questo esempio, io uso una velocità di trasmissione di 9600, facendo il mio contatore = 5208.

3

Ultimo, calcoliamo il nostro registro a scorrimento e finire di scrivere la nostra macchina dello Stato. Nel mio codice di esempio io uso un bit di start, bit di parità, 8 bit di dati e bit di fine. Si tratta di 11 bit totale.

Entrambe le immagini in fase 2 e 3 insieme nello stesso modulo completano il nostro codice trasmettitore necessario per programmare la FPGA. Questo codice funzionerà con un altro FPGA connessi in serie o con le finestre HyperTerminal tra l'altro hardware. Può essere facilmente modificabile con cui lavorare molto di più.

4 Ultimo, creiamo un dispositivo di prova per correggere eventuali errori e simulare il nostro programma prima di programmare il FPGA.

Questo conclude il trasmettitore. Si prega di lasciare commenti se avete domande o che ci sia qualcosa che manca qui.