April 16

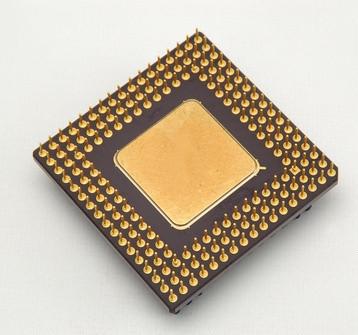

Molti corsi di livello universitario graduate- e in Very Large Scale Integration - VLSI - hanno progetti relativi ad uno o più aspetti della progettazione di microprocessori. L'obiettivo di questi progetti è quello di testare la capacità dello studente di applicare le conoscenze teoriche in un ambiente pratico. Tali progetti aiutano l'esperienza guadagno studente con software e gli strumenti utilizzati nella progettazione VLSI. L'obiettivo dovrebbe essere quello di mantenere i progetti abbastanza semplice in modo che lo studente possa completare in tempi ragionevoli, pur presentando una sfida per lo studente a pensare al di là del libro di testo.

In questo progetto, lo studente si prevede di creare un semplice processore RISC. L'articolo elabora sei istruzioni: addizione, sottrazione, moltiplicazione, divisione, carico e memorizzare. Assumiamo che ci sono tre registri: R1, R2 e R3. Le operazioni aritmetiche - cioè aggiungere, sottrarre, moltiplicare e dividere - vengono eseguite sui valori memorizzati nei registri R1 e R2. Pertanto, prima di eseguire l'operazione, i registri devono essere caricati. L'uscita del l'operazione verrà salvata nel registro R3. Prima di eseguire una nuova operazione, il valore di R3 deve essere conservato nella memoria.

Per questo progetto, una memoria dovrebbe essere attuato. La memoria può essere partizionato in dati e istruzioni porzione rispettivamente. Il processore RISC dovrebbe leggere istruzioni del istruzioni memoria dall'indirizzo 0x0 attraverso un valore massimo ed eseguire le azioni corrispondenti. La memoria può essere caricato con una serie di istruzioni per il test.

In questo progetto, il processore RISC di cui sopra dovrebbe essere implementato come un processore pipe-allineati. Un tipico processore RISC ha cinque stadi pipe-line:. "Fetch", "Decode", "Esegui", "Memory" e "riscrivere" Pipe-rivestimento consente a più istruzioni di essere attivi contemporaneamente, migliorando così le prestazioni del sistema.

processori tubi rivestito possono soffrire di bolle o cicli di tempo in cui non viene eseguita alcuna operazione utile. In un processore pipe-line ideale, si presume in tutte le fasi della tubazione completa in un tempo di ciclo, e non vi è alcuna dipendenza di una istruzione dall'altro. Tuttavia, a volte il risultato dell'operazione precedente può essere necessario per la successiva istruzione. In tali casi, nessuna operazione utile può essere eseguita finché la precedente istruzione completa. Gli studenti che alterano l'architettura del processore per ridurre al minimo questi cicli morti possono essere dato ulteriore credito.

Per questo progetto, diverse implementazioni delle funzioni aritmetiche possono essere studiati per cancello-count contro benefici prestazionali. Ad esempio, la vipera potrebbe essere implementato come un vipera ripple-carry o una vipera carry-look-ahead. Un sommatore ripple-carry ondulazione riporto da una fase aggiunta ad un'altra, e il risultato finale è disponibile quando l'ultimo stadio ha eseguito l'aggiunta. Questa tolleranza è lento nel senso che tiene molti cicli per il risultato sia disponibile. Tuttavia, il ripple carry-sommatore può essere implementato con un basso gate-count.

Una vipera carry-look-ahead determina il valore di riporto di un complemento prima del tempo. Poiché il valore di riporto è calcolato in anticipo, il sommatore può calcolare il risultato in meno cicli. Tuttavia, la vipera carry-look-ahead esegue più calcoli, e di conseguenza è alto sulla porta-count.

Il moltiplicatore potrebbe essere implementato come un moltiplicatore Booth o un moltiplicatore basato shift-add. Lo schema di base del cambio-add è il metodo di carta e matita regolare spostando e aggiungendo ripetutamente fino a quando il risultato è finalizzato. Il moltiplicatore Booth rappresenta il moltiplicatore in modo più ottimale di ridurre notevolmente il numero di aggiunte richiesti. Quindi, ci vuole meno il numero di cicli temporali per calcolare il risultato finale.

Un semplice controllo della cache può essere costruito. Il controller della cache potrebbe essere a quattro vie set-associativa, con un meno utilizzato di recente - LRU - basata su criteri di sostituzione. Quando un blocco di cache deve essere sostituito, la politica LRU sceglie il blocco di cache utilizzata meno di recente, e sostituisce il blocco.

In una cache set-associativa a quattro vie, ciascun blocco di memoria può essere posizionato in una delle quattro sedi nella cache. Rispetto alla cache direct-mapped in cui ogni blocco di memoria può essere situato in un luogo esattamente nella cache, il set-associative cache di quattro vie offre una maggiore flessibilità per la posizione di blocco e di conseguenza, migliori prestazioni della cache.

La cache dovrebbe essere attuata sia con write-back e le politiche write-through. Quando i dati nella cache vengono modificati, la politica write-back aggiorna la memoria principale solo quando il blocco di cache viene sostituito. D'altra parte, la politica write-through aggiorna la memoria ogni volta che i dati nella cache vengono modificati.

Un semplice sistema coerente di cache due processori con un invalido-modified-esclusiva-shared-based schema può essere implementato. Ogni processore avrà propria memoria cache. In questo schema, una linea o un blocco di memoria cache possono essere in uno dei quattro stati vale a dire, "modificati", "esclusivo", "condivise" o "non validi". Una linea è nello stato "modificato" se i dati in quella linea è valido solo nella cache del processore. Una linea è "esclusivo" se è presente nella cache del processore e nella memoria di dati in quella linea. Una linea è "condivisa" se i dati sono validi nella cache di entrambi i processori. Una linea è "non valido" se i dati non è valido nella cache del processore.

Sia la coerenza della cache basata su directory e snooping a base di coerenza della cache dovrebbero essere attuate, e la scalabilità di ogni algoritmo con l'aumentare il numero di processori dovrebbero essere studiati. Un meccanismo di coerenza della cache basata su directory mantiene una directory dello stato della cache nella memoria principale. Questa directory viene quindi utilizzato per inviare messaggi al processore sullo stato di ogni blocco di cache. In un sistema snoop-based, ogni modifica dei risultati blocchi della cache in un meccanismo di trasmissione con cui cache degli altri processori viene notificata circa il cambiamento nel blocco cache.