March 4

In tutta la storia del circuito integrato, la disposizione dei piedini del connettore metallico è cambiata. Poiché l'esigenza di trasferimenti di dati più grandi e veloci è aumentata, il grid array pin è evoluto per soddisfare questa esigenza.

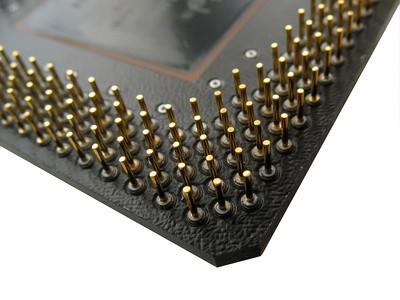

Il grid array staggered pin (SPGA) è una disposizione di perni su un circuito integrato in cui i perni sono disposti in file diagonali. Il modello viene anche descritto come quadrati intersezione.

Il vantaggio di utilizzare un sfalsata grid array pin, rispetto al precedente standard di righe e colonne allineate, è che il posizionamento SPGA permette perni più stretti, e quindi maggiori perni su una data superficie. Ciò può ridurre la dimensione di un microprocessore o di fornire maggiore capacità di trasferimento in un chip simile-size.

Nei circuiti integrati primi, i perni sono stati organizzati utilizzando il grid array pin (PGA) che fissano i perni in una formazione a griglia. Come processori avanzati e tenuti più pin, il PGA non era più adeguato. Il grid array staggered pin è stato creato per ridurre le dimensioni microprocessore quando è richiesto un gran numero di pin. Processori basati su Socket 5, Socket 7 e la tecnologia Socket 8 usano comunemente questa formazione.