December 19

Divisori alterano i segnali wireless e assistere con i segnali di decodifica ricevuti. Divisori svolgono funzioni matematiche nel nucleo logico di un computer. divisori di memoria, spesso collegati in serie con il segnale in ingresso da Internet, determinano la velocità di orologio di un computer. divisori seriali bit può essere utilizzato per eseguire l'analisi numerica all'interno di un computer.

Secondo "progettazione e la verifica dei microprocessori sistemi per applicazioni ad alta Assurance", "l'algoritmo di divisione Sweeney-Robertson-Tocher (SRT), grazie alla sua suscettibilità alle implementazione hardware efficiente, è onnipresente nei disegni microprocessori contemporanei." I interpreta algoritmo SRT suoi parametri come frazioni al fine di eseguire la divisione. Divisione dall'algoritmo SRT riferimento a una tabella di look-up per determinare la risposta risultante. I calcoli per questo algoritmo sono eseguite dalla logica unità aritmetica, che contiene un divisore in un'implementazione seriale.

divisori memoria utilizzano la frequenza di una rete di computer per determinare la frequenza di clock. Secondo "Embedded Systems design utilizzando il coniglio 3000 microprocessore" di Kamal Hyder, "i possibili divisori possono essere calcolate utilizzando le seguenti formule: divider = orologio / (32 x baud) - 1, e baud = orologio / (32 x (divisore +1)). "i microprocessori possono cambiare la loro velocità di clock riprogrammando i divisori o fare riferimento a una frequenza di funzionamento diverso.

generatori di forme d'onda creano segnali elettrici del modello di frequenza e uscita selezionata. Le forme d'onda vengono creati in un modello seriale con picchi a volte specificato. generatori di segnali utilizzano la memoria suddivisa per creare una varietà di forme d'onda. Secondo "Fondamenti di test elettronico per Digital, Memory, ea segnale misto VLSI Circuits", "commutazione l'orologio da un divisore ad un altro fornisce una frequenza-spostamento di fase continuo digitato segnale (FSK)".

Divisori convertire una frequenza di ingresso ad una frequenza di uscita inferiore dividendolo per un intero specificato N. Il segnale alla sua frequenza inferiore diviso viene inviato alla porta di uscita. divisori programmabili possono essere programmati con una vasta gamma di interi divisorie. "I test di produzione di RF e System-on-a-chip dispositivi per le comunicazioni wireless", dice, "per sistemi di comunicazione wireless, un limite massimo di 30.000 è posto su N a causa dell'introduzione di un eccessivo rumore di fase." I risultati del rumore di fase di rapida cambiamento di fase, creare interferenze con l'uscita del segnale.

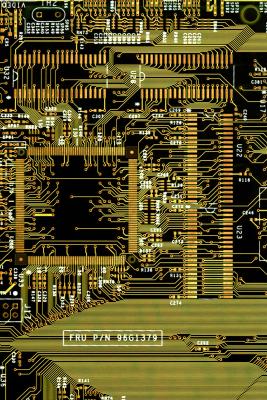

integrazione su vastissima scala (VLSI) circuiti contengono molti circuiti ad alta densità. La robustezza o la capacità del circuito di funzionare dopo un singolo guasto o guasti di serie viene testato utilizzando simulatori. CPU test circuito verificare la copertura funzione e la colpa dei circuiti di memoria, la ALU, il moltiplicatore, le unità di divisori e di controllo logico. I test iniziali verificherà la funzione di ogni unità in serie prima di testare guasti multipli. "Elementi essenziali di test elettronico per Digital, Memory, ea segnale misto VLSI Circuits", dice, "un simulatore di guasti seriale utilizza ripetutamente un simulatore vero valore."

Encoder alterano una forma d'onda per contenere informazioni codificate. Un decoder decifra le modifiche alla forma d'onda codificato per determinare il messaggio destinato. divisori polinomiali possono essere utilizzati come circuiti di decodifica.